集成電路版圖設(shè)計(jì) 芯片設(shè)計(jì)的物理實(shí)現(xiàn)藝術(shù)

在當(dāng)今信息時(shí)代的核心,集成電路(IC)構(gòu)成了所有電子設(shè)備的大腦與心臟。從智能手機(jī)到超級計(jì)算機(jī),從智能家居到航天器,其卓越性能的基石便是那精妙絕倫的集成電路設(shè)計(jì)。這一宏大工程通常被劃分為前后端,而集成電路版圖設(shè)計(jì),正是連接抽象電路構(gòu)想與實(shí)體硅芯片的橋梁,是芯片設(shè)計(jì)流程中至關(guān)重要的物理實(shí)現(xiàn)階段。

一、 集成電路設(shè)計(jì):從構(gòu)想到藍(lán)圖

在深入版圖設(shè)計(jì)之前,我們首先需要理解其上游環(huán)節(jié)——集成電路設(shè)計(jì)。這通常指邏輯設(shè)計(jì)或電路設(shè)計(jì),屬于設(shè)計(jì)流程的前端。

- 系統(tǒng)架構(gòu)與功能定義:設(shè)計(jì)始于明確芯片的規(guī)格,如處理速度、功耗、面積、功能模塊等。

- 寄存器傳輸級(RTL)設(shè)計(jì):工程師使用硬件描述語言(如Verilog或VHDL),以代碼的形式描述芯片各模塊的邏輯功能和數(shù)據(jù)流。此時(shí)的設(shè)計(jì)還是與工藝無關(guān)的抽象行為描述。

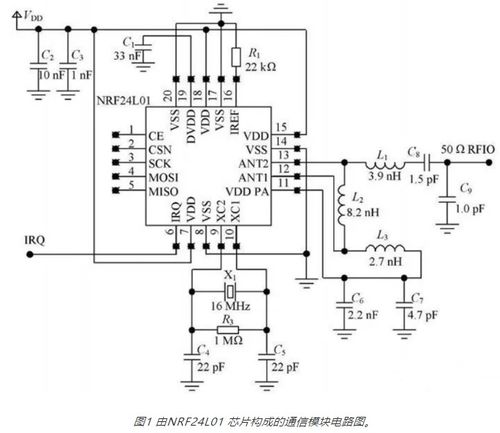

- 邏輯綜合:利用電子設(shè)計(jì)自動化(EDA)工具,將RTL代碼映射到特定的工藝庫(由芯片代工廠提供),生成門級的網(wǎng)表。這個(gè)網(wǎng)表是由標(biāo)準(zhǔn)邏輯門(如與門、或門、非門、觸發(fā)器等)及其連接關(guān)系構(gòu)成的電路圖。

至此,一個(gè)“應(yīng)該做什么”的功能性電路藍(lán)圖已經(jīng)完成,但它尚未告訴我們?nèi)绾卧诠杵稀拔锢淼亍睒?gòu)建它。這便是版圖設(shè)計(jì)的使命。

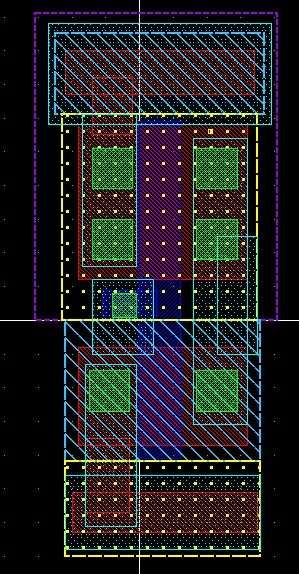

二、 集成電路版圖設(shè)計(jì):藍(lán)圖的物理雕刻

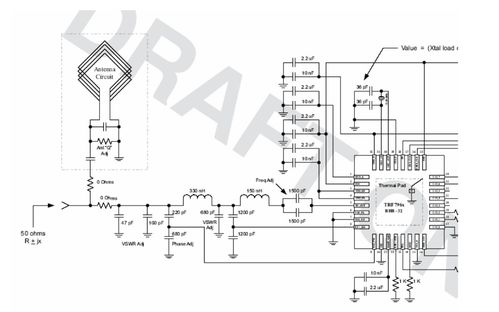

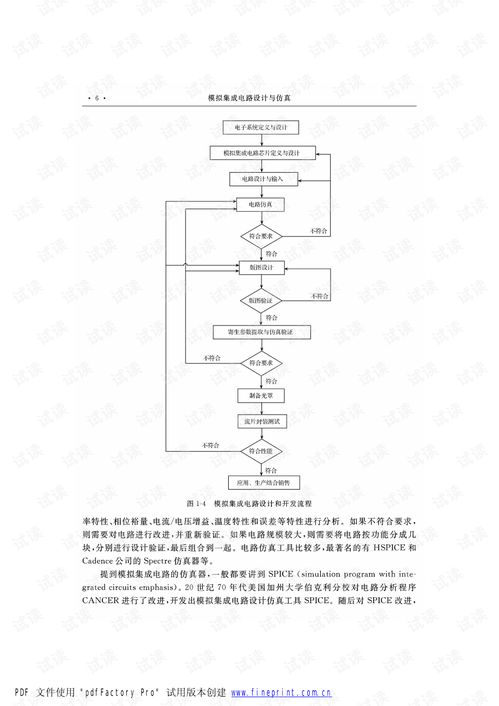

集成電路版圖設(shè)計(jì),又稱物理設(shè)計(jì),是將邏輯綜合后的門級網(wǎng)表,轉(zhuǎn)化為一系列可供芯片制造光刻使用的幾何圖形(版圖)的過程。這些圖形定義了硅片上每一層(如擴(kuò)散層、多晶硅層、金屬連接層等)的形狀、尺寸和位置。

其核心流程與挑戰(zhàn)包括:

- 布局規(guī)劃:如同城市規(guī)劃,需要確定芯片上各個(gè)大型功能模塊(如CPU核心、內(nèi)存控制器等)的擺放位置,規(guī)劃電源網(wǎng)絡(luò)和全局布線通道,以優(yōu)化芯片面積、信號時(shí)序和功耗。

- 標(biāo)準(zhǔn)單元布局:將網(wǎng)表中的數(shù)百萬甚至數(shù)十億個(gè)標(biāo)準(zhǔn)邏輯單元(如反相器、觸發(fā)器)合理地放置在芯片核心區(qū)域內(nèi),目標(biāo)是減少總布線長度和信號延遲。

- 時(shí)鐘樹綜合:構(gòu)建一個(gè)低偏移、低功耗的全局時(shí)鐘分布網(wǎng)絡(luò),確保芯片所有時(shí)序單元能在同一時(shí)刻精準(zhǔn)同步,這是高性能設(shè)計(jì)的關(guān)鍵。

- 布線:這是最復(fù)雜的步驟之一,負(fù)責(zé)用金屬線將所有單元按照網(wǎng)表連接起來。它必須遵守嚴(yán)格的設(shè)計(jì)規(guī)則,同時(shí)優(yōu)化信號完整性、串?dāng)_和電遷移等問題。現(xiàn)代芯片擁有十多層金屬互連,布線猶如在微觀世界進(jìn)行立體交通規(guī)劃。

- 物理驗(yàn)證:版圖完成后,必須經(jīng)過嚴(yán)格的驗(yàn)證:

- 設(shè)計(jì)規(guī)則檢查:確保版圖符合芯片代工廠的制造工藝極限(如最小線寬、最小間距)。

- 版圖與原理圖比對:確保物理版圖與原始邏輯網(wǎng)表在電氣連接上完全一致,杜絕任何錯(cuò)接、漏接。

- 電氣規(guī)則檢查:檢查天線效應(yīng)、短路、開路等潛在電氣問題。

- 后仿真與簽核:從最終版圖中提取出包含所有寄生電阻、電容的詳細(xì)參數(shù),進(jìn)行精確的時(shí)序、功耗和信號完整性分析。只有所有指標(biāo)均滿足要求,設(shè)計(jì)才能“簽核”并交付制造。

三、 設(shè)計(jì)與版圖:相輔相成,密不可分

集成電路設(shè)計(jì)與版圖設(shè)計(jì)并非割裂的環(huán)節(jié),而是深度迭代、緊密協(xié)作的關(guān)系:

- 前端指導(dǎo)后端:邏輯設(shè)計(jì)定義了電路的功能和性能目標(biāo),為版圖設(shè)計(jì)提供了根本依據(jù)。

- 后端反饋前端:在物理實(shí)現(xiàn)過程中發(fā)現(xiàn)的時(shí)序、功耗、面積等問題,會反饋給前端設(shè)計(jì)者,可能需要修改RTL代碼或架構(gòu)以進(jìn)行優(yōu)化。這種迭代是現(xiàn)代芯片設(shè)計(jì),尤其是高性能芯片設(shè)計(jì)的常態(tài)。

- EDA工具的紐帶:強(qiáng)大的EDA工具鏈貫穿始終,實(shí)現(xiàn)了從RTL到GDSII(最終版圖數(shù)據(jù)格式)的自動化或半自動化流程,極大提升了設(shè)計(jì)效率和可靠性。

###

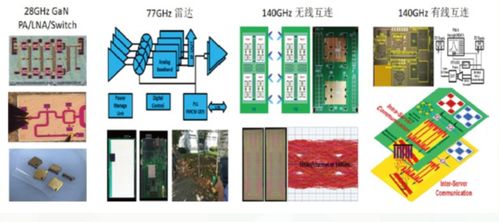

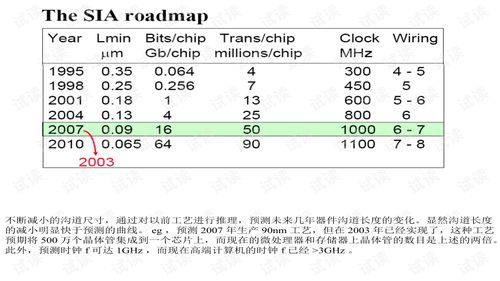

如果說集成電路設(shè)計(jì)是賦予芯片靈魂(功能)的樂章創(chuàng)作,那么集成電路版圖設(shè)計(jì)就是指揮樂團(tuán),將每個(gè)音符(晶體管和連線)精確安排在樂譜(硅片)上,最終演奏出完美交響樂的物理實(shí)現(xiàn)藝術(shù)。隨著工藝節(jié)點(diǎn)不斷微縮至納米乃至埃米尺度,版圖設(shè)計(jì)面臨的物理效應(yīng)挑戰(zhàn)日益嚴(yán)峻,其重要性愈發(fā)凸顯。正是這兩大領(lǐng)域的工程師們通力合作,在方寸之間進(jìn)行著人類最精密的創(chuàng)造,持續(xù)推動著計(jì)算能力的邊界,塑造著我們數(shù)字世界的未來。

如若轉(zhuǎn)載,請注明出處:http://www.thedeadconnection.com/product/72.html

更新時(shí)間:2026-02-19 11:34:40