基于NFC的無線通信系統集成電路設計

近場通信(NFC)技術作為一種短距離、高頻率的無線通信技術,已廣泛應用于移動支付、身份識別、智能家居等領域。其核心在于高效、低功耗的集成電路設計,這直接決定了整個系統的性能、可靠性與成本。本文將探討基于NFC的無線通信系統電路設計的核心模塊與關鍵技術,特別是集成電路層面的實現方案。

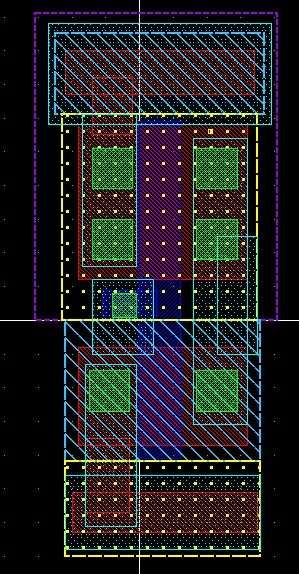

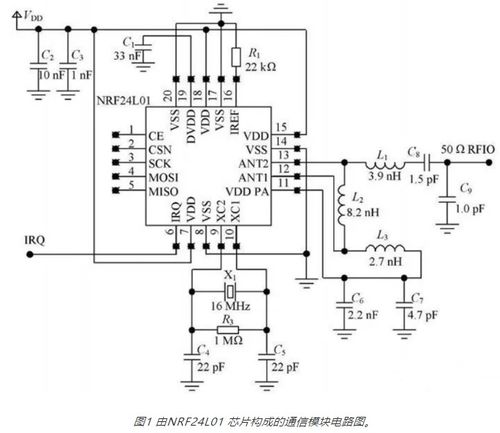

NFC系統的基本架構通常包括模擬前端(AFE)、數字基帶處理器、存儲器(如EEPROM)以及天線匹配網絡。其集成電路設計需在單芯片上高度集成這些模塊,并充分考慮與外部天線的接口。

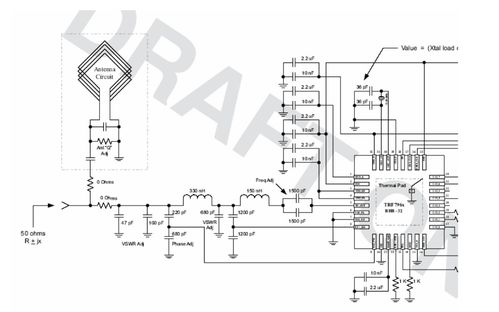

模擬前端電路是設計的重中之重。它主要包括射頻接收路徑、發射路徑和電源管理單元。接收路徑負責從天線拾取微弱的13.56MHz載波信號,經低噪聲放大器(LNA)放大后,通過包絡檢波或相干解調等方式恢復出數字基帶信號。發射路徑則通過負載調制或主動發射模式,將數字基帶信號調制到載波上,并通過功率放大器(PA)驅動天線。電源管理單元需高效地從射頻場中獲取能量(在無源模式下),為整個芯片供電,這需要精心設計整流器(通常采用倍壓或多級結構)和穩壓電路,以確保在變化的場強下提供穩定的工作電壓。

數字基帶處理器的設計關乎協議實現的效率與靈活性。它需要集成狀態機、編解碼器(如Miller、Manchester)、循環冗余校驗(CRC)模塊以及防沖突算法處理器。現代設計常采用可配置的處理器核(如ARM Cortex-M0)結合專用硬件加速器的方式,在保證處理速度的降低功耗并增強對多種NFC協議(如ISO/IEC 14443 Type A/B, FeliCa)的支持能力。

天線匹配網絡雖常作為片外分立元件,但其設計與芯片的輸入輸出阻抗緊密相關。集成電路設計時必須優化發射驅動器的輸出阻抗和接收器的輸入阻抗,以最大程度地減少片外匹配元件的數量與復雜度,降低整體方案成本并提高能量傳輸效率。

在集成電路的物理實現層面,面臨的主要挑戰包括:

- 低功耗設計:尤其是對于無源標簽芯片,所有電路必須在極低的功耗下工作。這需要采用特殊的低功耗邏輯、時鐘門控、電源域隔離等技術。

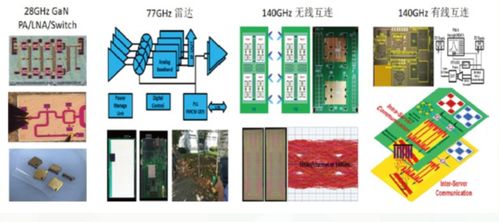

- 射頻性能優化:在深亞微米CMOS工藝下,設計高線性度、高效率的功率放大器和高靈敏度的低噪聲放大器,并處理好數字電路對敏感模擬電路的噪聲耦合。

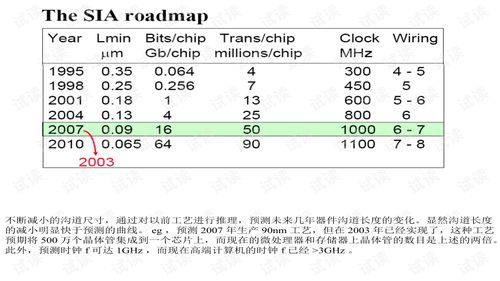

- 高集成度與成本控制:需要選擇合適的工藝節點(如0.18μm或0.13μm CMOS),在芯片面積、性能和成本之間取得平衡。

- 安全性與可靠性:對于支付等應用,需集成硬件加密引擎、真隨機數發生器(TRNG)和防側信道攻擊機制,同時確保芯片在ESD、RF場強突變等惡劣環境下穩定工作。

基于NFC的無線通信系統集成電路設計正朝著更高集成度(集成傳感器、顯示驅動等)、更低功耗(能量收集技術)、更強安全(集成安全元件SE)以及更廣泛的應用場景(如物聯網節點)發展。通過系統級架構優化、先進的混合信號設計方法和不斷演進的半導體工藝,NFC芯片將繼續為無縫、安全的無線連接提供核心動力。

如若轉載,請注明出處:http://www.thedeadconnection.com/product/70.html

更新時間:2026-02-19 20:34:58