095期集成電路設(shè)計精選科技成果推薦

隨著全球數(shù)字化轉(zhuǎn)型加速,集成電路(IC)作為信息產(chǎn)業(yè)的核心基石,其設(shè)計技術(shù)的創(chuàng)新與發(fā)展備受矚目。本期聚焦集成電路設(shè)計領(lǐng)域,精選了數(shù)項具有前瞻性與應(yīng)用潛力的科技成果,旨在為產(chǎn)業(yè)界和學(xué)術(shù)界提供參考與啟發(fā)。

1. 超低功耗人工智能邊緣計算芯片設(shè)計

該項成果針對物聯(lián)網(wǎng)終端設(shè)備的嚴(yán)苛功耗限制,提出了一種基于稀疏化神經(jīng)網(wǎng)絡(luò)與動態(tài)電壓頻率調(diào)整(DVFS)的芯片架構(gòu)。通過算法與硬件的協(xié)同優(yōu)化,在主流視覺識別任務(wù)中,其能效比達到15 TOPS/W,相比傳統(tǒng)設(shè)計提升約3倍,同時保持了高識別精度。該芯片可廣泛應(yīng)用于智能安防、可穿戴設(shè)備及工業(yè)傳感節(jié)點,顯著延長設(shè)備續(xù)航時間。

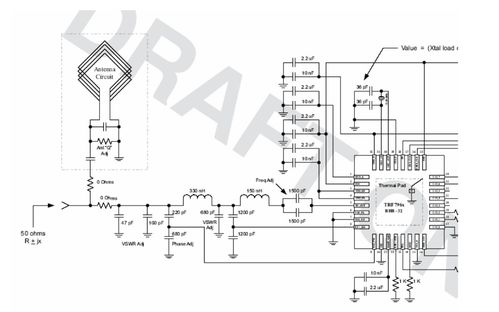

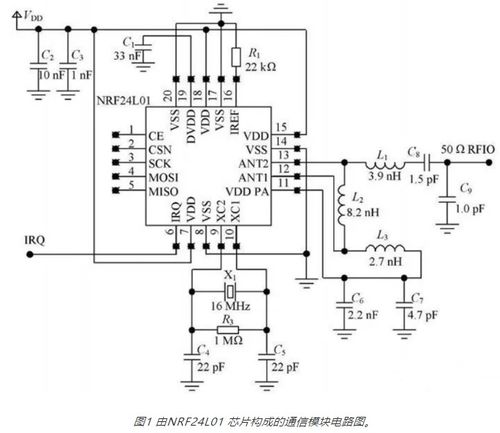

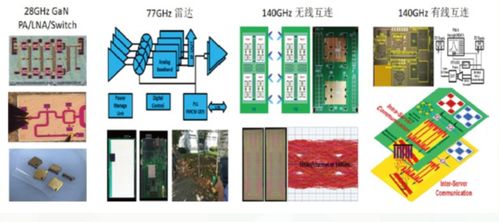

2. 面向5G/6G通信的高性能射頻前端集成方案

本技術(shù)攻克了高頻、高線性度與高集成度難以兼得的難題,采用新型硅基化合物半導(dǎo)體異質(zhì)集成工藝,將功率放大器(PA)、低噪聲放大器(LNA)及開關(guān)等模塊 monolithic 集成。實測顯示,在28GHz頻段下,其輸出功率達到27dBm,效率超過40%,同時噪聲系數(shù)低于3dB。該方案為下一代通信設(shè)備的小型化與高性能化提供了關(guān)鍵支持。

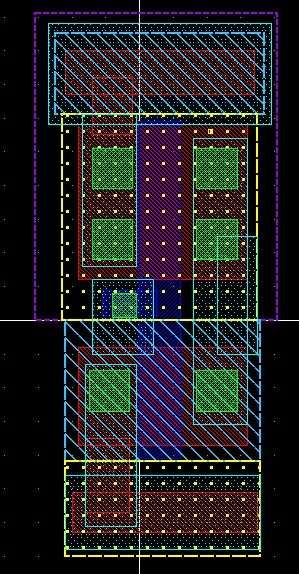

3. 基于存算一體架構(gòu)的深度學(xué)習(xí)加速器

突破傳統(tǒng)馮·諾依曼架構(gòu)的“內(nèi)存墻”瓶頸,該設(shè)計利用電阻式存儲器(ReRAM)實現(xiàn)模擬域乘加運算,將數(shù)據(jù)存儲與處理在物理層面融合。測試芯片在ResNet-50網(wǎng)絡(luò)推理中,相比同工藝GPU,能效提升達兩個數(shù)量級,延遲降低90%。該技術(shù)特別適合數(shù)據(jù)中心、自動駕駛等對實時性與能效要求極高的場景。

4. 汽車電子功能安全芯片設(shè)計平臺

遵循ISO 26262 ASIL-D最高安全等級標(biāo)準(zhǔn),該平臺提供了從架構(gòu)、設(shè)計、驗證到故障注入測試的全套工具鏈與方法學(xué)。其核心包括鎖步雙核處理器、安全監(jiān)控單元及錯誤糾正碼(ECC)內(nèi)存控制器,可系統(tǒng)性檢測并緩解隨機硬件故障。已成功應(yīng)用于多款國產(chǎn)智能駕駛控制器芯片,助力提升汽車電子系統(tǒng)的可靠性。

5. 開源高性能RISC-V處理器核及生態(tài)工具

該項目推出了一款主頻可達2GHz的64位多核RISC-V處理器IP,采用12nm工藝實現(xiàn),并配套提供完整的軟件開發(fā)套件(SDK)與驗證環(huán)境。其微架構(gòu)支持亂序執(zhí)行與矢量擴展,性能對標(biāo)國際主流中高端內(nèi)核。該開源項目降低了芯片設(shè)計門檻,為國內(nèi)IC設(shè)計企業(yè)提供了自主可控的處理器基礎(chǔ)選擇,促進產(chǎn)業(yè)生態(tài)繁榮。

與展望

本期推薦的科技成果涵蓋了人工智能、通信、計算架構(gòu)、汽車電子及處理器生態(tài)等集成電路設(shè)計的關(guān)鍵方向,體現(xiàn)了向“更低功耗、更高性能、更強智能、更安全可靠”持續(xù)演進的技術(shù)趨勢。這些成果不僅具有扎實的理論創(chuàng)新,更展現(xiàn)出明確的產(chǎn)業(yè)化應(yīng)用前景。隨著工藝演進與系統(tǒng)需求復(fù)雜化,跨學(xué)科協(xié)同、軟硬件協(xié)同與開放生態(tài)建設(shè),將成為推動集成電路設(shè)計突破的核心動力。

如若轉(zhuǎn)載,請注明出處:http://www.thedeadconnection.com/product/71.html

更新時間:2026-02-19 16:37:49